知识点:静电放电敏感度 一、ESD带电器件模型 带电器件模型(Charged-Device Model - CDM)是第三种重要的元器件静电放电耐受阈值的测试方法。CDM 模型与之前讨论的HBM、 MM模型完全不同。HBM和MM模型是模拟人体(Human Body)或机器设备(Machine)带电后对元器件放电,而 CDM模型则是模拟元器件本身带电后对地放电。随着芯片制造、封测、装联的自动化程度提高,人体接触器件的机会相对减少,带电器件ESD放电事件越来越成为微电子器件失效的主要原因之一。

知识点:静电放电敏感度

一、ESD带电器件模型

带电器件模型(Charged-Device Model - CDM)是第三种重要的元器件静电放电耐受阈值的测试方法。CDM 模型与之前讨论的HBM、 MM模型完全不同。HBM和MM模型是模拟人体(Human Body)或机器设备(Machine)带电后对元器件放电,而 CDM模型则是模拟元器件本身带电后对地放电。随着芯片制造、封测、装联的自动化程度提高,人体接触器件的机会相对减少,带电器件ESD放电事件越来越成为微电子器件失效的主要原因之一。

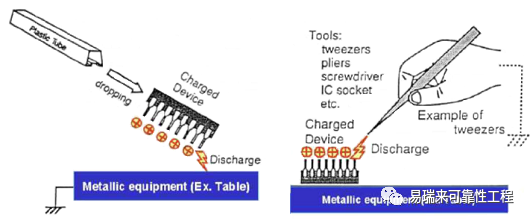

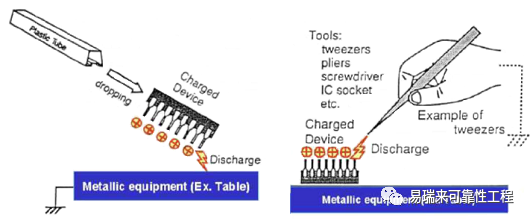

半导体器件在装配、试验、测试、运输及存贮过程中由于IC管壳(封装)与其它绝缘材料(如包装用的塑料袋、塑料管)相互磨擦,就会使芯片管壳带电。器件本身作为电容器的一个极板而存贮电荷。下图示意了从塑料包装管中滑落的芯片因摩擦带上了正电荷静电,当引脚接触到接地的金属设备或被接地的人体用金属镊子触碰引脚的瞬间,形成导电通道,放电电流流经IC内部,导致芯片损伤。此种模型的放电时间较HBM模型或MM模型更短,仅约几纳秒(ns)之内。

CDM模型就是基于已带电的器件通过引脚与地接触时,发生对地放电引起器件失效而建立的。带电器件的电容值与器件的封装结构、引脚排列形式及器件放置时的方位等因数有关,一般仅为几到几十皮法(pF)。元器件管芯(component)的CDM灵敏度非常依赖于封装。对于完全相同的IC晶片(chip),采用小型封装(SOP)可能比双列直排(DIL)封装中的IC更容易受到CDM损坏。采用薄型小型封装(TSOP)或引脚阵列(PGA)封装的IC通常具有最低的CDM耐压能力。CDM ESD波形的上升时间极短(ps-皮秒级),峰值电流很大 (5~20A/500V),维持时间极短(0.5~1ns),一般保护电路甚至来不及起作用。

2KV HBM、 200V MM、 与1KV CDM的放电电流比较(如上图2),其中1KV CDM的放电电流在不到1ns的时间内,便已冲到约15安培的尖峰值,其放电的总时段约在10ns内便结束了。此种放电方式更易造成集成电路的损伤。

为了表征器件本身带静电并放电的电路特性,以及半导体器件的ESD敏感度,相关标准组织/机构制定了带电器件模型,以规范CDM模式下的ESD测试模型和等级标准。

以上相关的标准有所差异且被多次修订,但原理基本一致,本文以经典的JESD 22标准为主要参考进行说明。

JESD22-C101标准文本的完整名称为:“Field-Induced Charged-Device Model Test Method for Electrostatic- Discharge-Withstand Thresholds of Microelectronic Components”。直译为:“微电子元器件静电放电耐受阈值的电场感应带电器件模型测试方法”。

该标准描述了建立带电器件模型 (CDM) 静电放电 (ESD) 耐受阈值的统一方法。

-

带电器件模型(CDM):是用于描述、当器件通过摩擦起电或因静电感应而获得电荷,然后突然

接触接地物体或表面时、 发生ESD 事件的一种特定的电路特征。

-

静电放电 (ESD):静电电荷在处于不同静电势的物体之间的突然转移。

-

场感应充电(Field-induced charging):利用静电感应的一种电荷产生方式。

【编者按:】如此看来,JESD22-C101标准文本的标题名称似乎未将摩擦起电或其它导致器件带电的方式表述在内。实际上为了规范描述CDM模型和量化测定,该标准中的CDM测试模拟装置(图4)是以电场感应充电方式设计的,故而如此命名。

所有带封装的半导体元器件、薄膜电路、表面声波 (SAW) 组件、光电组件、混合集成电路 (HIC) 和包含任何这些元器件的多芯片模组 (MCM) 都可根据该标准进行评估。该标准中描述的测试方法也可用于评估被运输的晶圆(wafer)或裸片(bare chips),但在实施测试时,这些元器件(components)必须被组装到类似于最终应用的封装中。对于无封装的裸片则不适用于本标准。

CDM模型的充电方式有两种:直接充电和电场感应充电,如图3所示。通过电场感应对DUT进行充电,避免了直接充电可能损伤器件的情况发生,因此,大多数测试标准推荐采用感应充电方式。

依据JESD22-C101F (Oct, 2013)标准的CDM模型采用了电场感应方式充电,其测试电路如下图4所示。

图4 电场感应CDM模拟测试装置电路图 & 等效电路

可拆卸放电头用于启动放电,该放电头由弹簧探针、径向电阻、顶部接地平面、半刚性同轴电缆和支撑臂组成。顶部接地平面应为方形导电板,边长为63.5 mm±6.35 mm(2.5 in±0.25 in)。放电路径包括1个至少3 GHz带宽的1欧姆电阻电流探针,用于监测放电波形。从1欧姆电阻到示波器的线缆也应具有至少3 GHz的带宽。FR-4电介质的厚度应为0.381 mm±0.038 mm(0.015 in±0.0015 in),电介质的介电常数应规定为4.7(±5%)@1 MHz。图4所示充电限流电阻标称为100 MΩ或更大,但更大的电阻需要延长每次测试放电之间的时间以确保待测器件被饱和充电。感应充电电极的尺寸应大于器件的尺寸(ESD STM5.3.1标准文本则明确要求充电极板的面积至少是待测器件面积的7倍以上)。FR-4电介质的面积应等于或大于充电极板。模拟测试装置应尽量减小充电和放电路径的寄生参数,这些寄生参数会对测试结果造成显著的影响。

CDM测试模拟装置在进行正式测试使用前,需要进行校验标定。校验用的标准测试组件(Standard Test modules)包括一小一大两个圆片(disk),其尺寸及特性要求如下表1(Table 1)。

圆片是由黄铜制成,其表面镀有镍或金/镍、或镍上镀金。圆片周长上必须光滑无毛刺、以免测试时产生电弧影响测试结果。大、小圆片放置在FR-4电介质/充电极板上的电容值需要被测定且满足表1中的规格。

CDM测试模拟装置的校验测试有3个层级,测试要求如表2(Table 2)所述。

-CDM Equipment Manufacturer Qualification (CDM 测试装置生产厂家质检)

-User Verification (使用者校验)

-Routine Verification (例行校验)

使用标准测试组件,对CDM测试模拟装置按表3(Table 3)要求进行以下4项测试校验,其脉冲波形如图6。

图6 Waveform Specification

校验测试过程如下:

1)将标准测试组件的电位提高到表3所示的电压;

2)使标准测试组件在正极性和负极性下至少放电三次;

3)使用示波器记录波形,并取表3中规定参数的平均值;

4)根据需要,对其它放电头重复上述步骤1-3;

5)如果波形特征不符合表3的要求,则应清洁测试组件(在超声波清洗槽中使用异丙醇清洗圆片约20秒,并用中性气流使其干燥,以防止测试操作期间电荷泄漏)后并重复上述步骤1-3;

6)如果波形仍不能满足表3的要求,则之前的校验测试数据都应作废,并对模拟装置进行检修。

JESD22-C101标准推荐的CDM ESD测试的电压水平为:125V、250V、500V、1000V。不建议进行超过1000V的测试。

*注:也可以使用本标准以前版本中推荐的电压水平(100 V、200 V、500 V和1000 V)。

为了更精确地确定器件的CDM ESD阈值,除了上述建议的电压外,还允许在>=100 V和<=1000 V的任何电压水平下进行测试。

测试应在室温下进行,环境湿度不应超过60%RH。测试可以在以上列出的任何可行的电压水平开始。除非另有规定,通常每次测试取3个被验证合格的器件为样本。

对于每个器件样本,向其各个引脚施加至少一个正极和至少一个负极放电。在两次放电之间允许间隔足够的时间(>200 ms),以使器件充分感应带电至测试的电压水平。通过监视放电过程探测器的输出或将示波器连接到电流检测电阻器上,验证是否出现对应极性的放电脉冲。

放电应力可以按极性划分,对应每个极性(正向放电或负向放电)都应使用至少3个样本。如果器件的每个管脚至少属于某一个管脚组合中的一个,也可以将该管脚划分到一个或多个管脚组合。每个管脚组合也应该至少对应3个样本。

如果在某一电平下施加应力的所有3个样本都通过了,则认为该器件“通过”了该电压水平。这些器件样本仍然可以继续在其它电压水平上进行测试,直至一个或多个样本在其它的某一电压电平下失效。未通过测试的器件样本不得用于其它级别的测试。当然也可以针对任一电压水平用新的器件样本进行测试。

规定数量的样本(通常为3个)进行放电应力测试全部所能通过的最高电压水平即为该器件的CDM耐受阈值。此外,在低于耐受阈值的任何测试电压水平之下,不得发生任何样品失效。如果器件样本未通过任何电压水平测试,则其阈值为0 V。

所有样本都必须满足以上测试要求,直至达到特定的电压等级(Voltage Level),才能将该种器件归类为如下特定的静电敏感度分级(sensitivity classification)。

ESD STM5.3.1标准扩展了

JESD22-A101的CDM分级,具体见其标准中之Table 2,如下:

HBM、MM、CDM三种测试模型都是针对半导体器件受ESD影响而建立的。上述ESD测试模型的测试方法对元器件都具有破坏性。这些测试模型用于标定静电放电敏感半导体元器件的失效阈值。对于电子系统或整机产品的ESD测试标准则主要遵照“国际电工委员会-IEC”制定的IEC61000-4-2标准,此将在后续另文介绍。

相关推荐链接:

1、防静电接地施工工艺变压器局部放电与套管连接部位电场的分析

2、静电防护培训